摘要:在對更快、更小和更高性能的電子設(shè)備的需求驅(qū)動下,微電子工業(yè)高速發(fā)展。集成電路的特征尺寸以及用于不同電路之間連接的印刷電路板的尺寸都在不斷縮小,使得很多傳統(tǒng)微電子材料與技術(shù)都面臨巨大的挑戰(zhàn),需要通過新材料、新技術(shù)的研究與應(yīng)用,從而保證微電子行業(yè)的可持續(xù)快速發(fā)展。 集成電路的互補型金屬-氧化物-半導(dǎo)體CMOS技術(shù)中,傳統(tǒng)的SiO2柵介電材料已經(jīng)逼近其厚度極限,尋找新型高介電常數(shù)的替代材料,是半導(dǎo)體工業(yè)迫在眉睫的任務(wù)。多種高介電柵介質(zhì)候選材料得到廣泛研究。其中,氧化鉿(HfO2)已成為高介電柵介質(zhì)的最有希望的競選材料之一,是當(dāng)前high-k材料研究的熱點。然而,單一HfO2存在結(jié)晶溫度較低、易在界面處形成低介電常數(shù)硅酸鹽、載流子遷移率低等問題。人們通過在HfO2中摻入N、Si、Al、Ti、Zr等元素來提高其性能。與半導(dǎo)體工藝兼容的原子層沉積(ALD)和化學(xué)氣相沉積(CVD)方法已成為制備high-k薄膜最主要的兩種技術(shù),有機前驅(qū)體帶來的碳污染問題是限制ALD和CVD薄膜性能提高的重要因素。本文選取Hf-Al-O和Hf-Zr-O復(fù)合薄膜,以無水硝酸鹽為前驅(qū)體,采用ALD和CVD方法制備了這兩種復(fù)合薄膜,對其生長特性、薄膜成分與結(jié)構(gòu)、熱穩(wěn)定性和電學(xué)性能等,進行了較為深入的研究。 快閃存儲器是目前非揮發(fā)性存儲器的主流器件。但隨著器件尺寸的不斷縮小,基于傳統(tǒng)浮柵結(jié)構(gòu)的快閃存儲器在繼續(xù)等比例縮小方面受阻,新型電荷俘獲存儲器成為下一代快閃存儲器的有力競爭者。傳統(tǒng)的電荷俘獲型存儲器以SONOS (Si/SiO2/Si3N4/SiO2/Si)結(jié)構(gòu)為代表,但其較差的保持性能是制約其進一步發(fā)展的關(guān)鍵。因此,很多半導(dǎo)體公司和研究機構(gòu)致力于對傳統(tǒng)SONOS結(jié)構(gòu)中的隧穿層、電荷俘獲層、阻擋層等進行改進,以獲得新型電荷俘獲型存儲器,使得其在具有較好的保持性能下,能有更快的編程/擦除速度和更低的操作電壓。

本文采用分子原子沉積(MAD)技術(shù)制備Al2O3薄膜,作為隧穿層和阻擋層,獲得MANAS (Metal/Al2O3/SiNx/Al2O3/Si)新型電荷俘獲型存儲器,對存儲器的存儲與保持性能以及Al2O3薄膜的結(jié)構(gòu)與電學(xué)性能進行了深入的分析研究。 隨著微電子工業(yè)的不斷發(fā)展,用于電路之間連接的印刷電路板也不斷向高密度和小型化的方向發(fā)展。與微通孔技術(shù)相結(jié)合的積層多層板技術(shù)中,用于連接層間線路的通孔也變得越來越小,深徑比越來越大,對填充于微通孔中電鍍銅的性能要求也越來越高。由于微觀結(jié)構(gòu)對宏觀性能的影響巨大,所以對電鍍銅微觀結(jié)構(gòu)的研究也成為微電子工業(yè)關(guān)注的熱點。此外,電鍍銅在電鍍完成后,于室溫下會發(fā)生所謂“自退火”現(xiàn)象,對電鍍銅的結(jié)構(gòu)、取向以及宏觀性能等產(chǎn)生了很大的影響,因此對電鍍銅自退火現(xiàn)象的研究也深受關(guān)注。本文采用多種分析表征手段,對印刷電路板微通孔中的電鍍銅微觀結(jié)構(gòu)進行了表征研究,同時追蹤了電鍍銅的自退火過程,并對此過程中晶粒取向的變化進行分析討論。

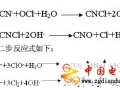

本論文主要成果如下: 1.成功合成了具有良好揮發(fā)性且不含碳的無水硝酸鉿和鉿鋯復(fù)合硝酸鹽,以無水硝酸鉿作為Hf源,以TMA為Al源、H20為氧源,用ALD方法制備了Hf-Al-O復(fù)合薄膜。改變薄膜中Hf的含量,薄膜的等效氧化物厚度、平帶電壓、電壓回滯、漏電流等電學(xué)性能指標(biāo)也隨之線性變化。無水鉿鋯復(fù)合硝酸鹽中的硝酸鉿和硝酸鋯主要以固溶體的形式存在,Hf/Zr組分比為1.72:1。采用此復(fù)合前驅(qū)體,分別用ALD和CVD方法成功沉積了Hf-Zr-O復(fù)合薄膜,并研究了薄膜的各項性能。其中,ALD方法制備的薄膜中Hf/Zr組分比約為1:4,與復(fù)合前驅(qū)體中的組分比差別較大;而CVD薄膜中Hf/Zr組分比與前驅(qū)體中的非常吻合。我們認為同一復(fù)合前驅(qū)體在不同沉積方法中的不同表現(xiàn)可能源于兩種沉積技術(shù)不同的沉積原理以及對反應(yīng)前驅(qū)體的不同要求。CVD方法制備Hf-Zr-O復(fù)合薄膜的結(jié)果表明無水鉿鋯復(fù)合硝酸鹽是一種有效的沉積雙金屬氧化物的無機前驅(qū)體,其蒸氣可以同時穩(wěn)定地輸運兩種金屬元素。

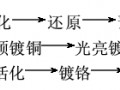

2.采用MAD方法生長trap-less的Al2O3 (MAD_Al2O3),取代SONOS結(jié)構(gòu)中的隧穿層和阻擋層SiO2,制備出MANAS型電荷俘獲存儲器結(jié)構(gòu)單元。MAD_Al2O3薄膜的電學(xué)和結(jié)構(gòu)成分測試表明,薄膜與Si襯底之間具有平整的界面和低的界面態(tài)密度,以及相對較高的導(dǎo)帶偏移量(3.9eV)和較低的價帶偏移量(2.1eV),并且薄膜的J-V曲線與溫度無關(guān),幾乎沒有電場應(yīng)力誘導(dǎo)漏電流的存在,可認為薄膜中沒有電荷陷阱,電荷傳輸符合FN隧穿機制。由于隧穿層和阻擋層的優(yōu)異性能,MANAS型存儲器實現(xiàn)了FN隧穿機制的編程/擦除操作,經(jīng)過+12V/100μs的編程脈沖即實現(xiàn)5.6V的編程窗口,-12V/10ms的擦除脈沖獲得6V的擦除窗口,且沒有擦除飽和現(xiàn)象。MANAS型存儲器僅用±11V的操作電壓就可以實現(xiàn)目前最先進SONOS型非揮發(fā)存儲單元需要士17V才可以達到的編程/擦除窗口;并且經(jīng)過105個編程/擦除循環(huán)后,存儲窗口幾乎沒有什么變化,具有很好的耐久性能。此外,MANAS型存儲器對數(shù)據(jù)具有優(yōu)異的保持性能,在從室溫到2500C的高溫下,分別經(jīng)過+10V/100μs的編程脈沖和-10V/10ms的擦除脈沖后,在1-104sec的時間范圍內(nèi)其衰退速率分別僅為-0.24V/dec和+0.11V/dec,并且在10-4_1 sec的短時間內(nèi)也具有很好的保持特性。

3.采用背散射電子衍射(EBSD)和聚焦離子束(FIB)等方法,對用于微通孔的電鍍銅進行了微觀結(jié)構(gòu)的表征,比較了使用不同添加劑A、B、C電鍍的銅樣品在經(jīng)過浮焊測試后的不同表現(xiàn):采用添加劑A和B的電鍍銅樣品在通孔拐角處出現(xiàn)了細小裂紋,且只在互連銅內(nèi)延伸一小段即終止,表現(xiàn)出良好的抗高溫性能;而采用添加劑C電鍍的銅樣品通孔中的化學(xué)鍍銅和電鍍銅出現(xiàn)很大的裂縫,貫穿整個電鍍層,使鍍層幾乎被割裂開,表明其承受高溫的能力較弱。采用X射線衍射(XRD)技術(shù),追蹤了一定條件下制備的電鍍銅樣品的自退火過程,并結(jié)合EBSD技術(shù),對此過程中電鍍銅的結(jié)構(gòu)變化進行了表征。發(fā)現(xiàn)電鍍銅樣品經(jīng)過自退火,發(fā)生了從110織構(gòu)到311織構(gòu)的轉(zhuǎn)變。對這一轉(zhuǎn)變的機制進行了仔細研究,并將此變化過程解釋為:電鍍液中的添加劑、電鍍參數(shù)和110晶向為主的多晶襯底銅等因素綜合作用,使得剛電鍍完的多晶銅樣品以110晶向為主;經(jīng)過“自恢復(fù)”階段后,電鍍銅的晶粒長大,同時多晶樣品中的110晶向先通過孿晶變化關(guān)系而轉(zhuǎn)變?yōu)?11晶向,接著在減小表面能的驅(qū)動下,再轉(zhuǎn)過6°變?yōu)?11晶向,從而實現(xiàn)電鍍銅樣品從110織構(gòu)到311織構(gòu)的轉(zhuǎn)變。 集成電路作為信息產(chǎn)業(yè)的基礎(chǔ)和核心,已成為當(dāng)前國際競爭的焦點和衡量一個國家綜合國力的重要標(biāo)志。國家科技重大專項《極大規(guī)模集成電路制造裝備及成套工藝》于2009年啟動,目前,在這一領(lǐng)域我國擁有的自主知識產(chǎn)權(quán)的材料與技術(shù)嚴重不足。

本論文的工作集中研究的幾種微電子材料的制備、表征與性能,對探索新型微電子材料在下一代集成電路中的應(yīng)用,促進我國集成電路的發(fā)展,具有重要參考價值。